# A Study on Run Time Assurance for Complex Cyber Physical Systems

Matthew Clark, Xenofon Koutsoukos, Ratnesh Kumar, Insup Lee, George Pappas, Lee Pike, Joseph Porter, Oleg Sokolsky

April 18, 2013

# Contents

| 1 | Introduction                                                                                                                                                                                                                                                                                                                                          |                                  |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|   | Matthew Clark                                                                                                                                                                                                                                                                                                                                         | 3                                |

| 2 | State of the Art in Run Time Assurance Boundary MethodsDr. George Pappas and Dr. Ratnesh Kumar2.1 Example: Aircraft conflict resolution2.2 Computability boundary2.3 Discrete abstractions2.4 Reachability computations2.5 Barrier certificate methods2.6 Verification using robust simulation2.7 Computational tools2.8 Run-Time Assurance Framework | 9<br>9<br>12<br>14<br>15<br>16   |

| 3 | State of the Art for Runtime Monitoring and SwitchingDr. Insup Lee and Dr. Oleg Sokolsky3.13.2Categories of runtime monitoring and switching3.3Instrumentation3.4Overhead reduction3.5Feedback and recovery3.6Challenges in applying runtime monitoring and switching in RTA                                                                          | 22<br>25<br>26<br>27             |

| 4 | Timing Constraints and Worst Case Execution TimeDr. Lee Pike4.1 Timing Concepts4.2 Timing-Aware RTA4.3 Recommended Future Research                                                                                                                                                                                                                    | 32                               |

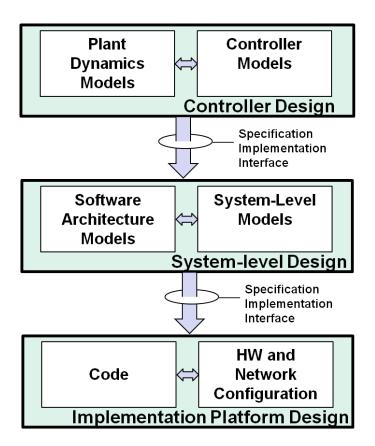

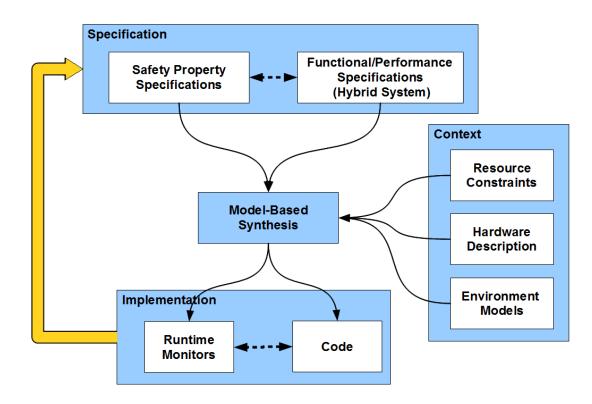

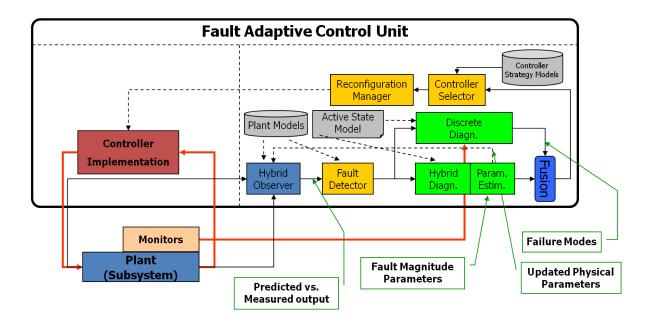

| 5 | State of the Art in Model Based Design for RTADr. Xenofon Koutsoukos and Dr. Joseph Porter5.1Research Objectives5.2Modeling Frameworks and Languages5.3Software Design5.4Behavioral Analysis5.5Dependability Analysis5.6Model-based testing5.7Applications and Evaluation5.8Challenges                                                                | 42<br>45<br>46<br>50<br>52<br>54 |

# 1 Introduction

#### Matthew Clark

Cyber-physical systems are becoming more and more complex, thereby increasing the cost and time to ensure safety. They range from highly complex but finite state to infinite state, indeterminate systems. Current methods of performing software and system verification and validation requires exhaustive offline testing of every possible state space scenario; an impossible task for adaptive, non-deterministic, and near infinite state algorithms. This certification incapacity is creating a growing gap between state of the art software system capabilities and capabilities of systems which can be certified. Currently, we attempt to prove systems are correct via verification of every possible state PRIOR to fielding the system. However, if, through the use of run time architecture, we can provably bound systems behavior, then it may be possible to reduce the reliance on comprehensive off-line verification, shifting the analysis/test burden to the more provable run time assurance mechanism.

Consider autonomy as "the ability to reason and make decisions to reach given goals based on a systems current knowledge and its perception of the variable environment in which it evolves[1]." Autonomous, safety critical software that relies on the perception of its environment to make decisions quickly becomes a large near infinite state problem. To that end, Run Time Assurance (RTA) is the ability to ensure the safe operation of a system that contains functional components, which may not be sufficiently reliable, or sufficiently verified, according to current development or certification standards. There may be multiple reasons for having such components in a system: under the normal conditions, they can provide improved performance or operational efficiency for the system, or enhance the user experience. The core idea that enables the use of such components in a system is the presence of a safe fallback mechanism that:

1) Reliably detects potential problems

2) Invokes a recovery/switching mechanism that can ensure safe operation of the system, possibly with reduced capabilities and performance.

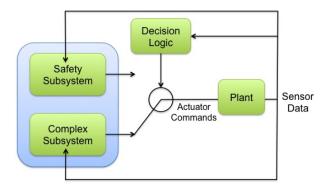

Figure 1: Run Time Assurance of Unverified Flight Critical Software

Within the flight domain, the following certification challenges were identified as only solvable at run time: unanticipated vehicle interactions, unanticipated external interactions, mission/battle management decisions with flight-critical consequences, untested system modes, and autonomous decision making control [1]. The desire is that unmanned aerial systems (UAS's) should be able to use the same infrastructure as manned systems, with minimized uniqueness. They also must be made to be responsive to dynamic missions, adapting in real time to changes in environment, mission, etc. This creates an unsolvable offline certification challenge but an opportunity for run time certification techniques.

Similarly, in the automotive sector, the Google autonomous car has successfully achieved over 100,000 miles of unattended driving in the streets of California [2]. Google has heralded the innovation as "safer than human driving while intoxicated." But up to this point, as required by California state law, a human driver must be present in the vehicle who has the ability to monitor and intervene the autonomous system in case of a failure. For the autonomous vehicle scenario to become reality, the human monitor must be replaced with a certified bounding algorithm that is capable of providing absolute guarantees on the vehicle's safety in the highly dynamic environment such as urban streets.

Within the power distribution industry, innovations in smart-grid technology consider decentralizing power distribution by creating stand-alone power units called "micro-grids." Users would have more control with these units and would have the option to add alternate power sources such as windmills or solar panels. Advantages of micro-grids include versatility, the ability to better align protection with the usage of alternative energy sources, and the relatively small vulnerability to security threats as compared to the current centralized power distribution system. However, the de-centralized "micro-grid" is an inherently unstable control system that needs to be closely monitored to prevent supply over-voltage or sagging [3] . To enable the combined use of the micro-grid, highly adaptive autonomous systems would be needed to carefully manage energy production and consumption and would require a boundary mechanism to assure safety of the system.

Finally, the NITRD report on 21st century medical devices cited the need for adaptive patientspecific algorithms. Current devices are designed to cover a large group of patients with similar medical conditions. Medical devices that adapt to a patient's specific medical condition would improve the quality of patient care. These medical devices may be more responsive to specific patient needs but must not broach a boundary that will cause harm [4].

As early as 2002, Run Time Assurance was identified as a key technology to increase the reliance on online certification. Barron Associates and Lockheed Martin developed the original concept of "Run Time Assurance." They described RTA as a "mechanism for the implementation of advanced, complex flight control functions". The approach was similar to the Simplex architecture developed by the Software Engineering Institute at Carnegie Mellon University Both the RTA and Simplex concepts focused on verifying that an advanced controller performs within a pre-described boundary and predicts violations of the boundary in enough time to safely switch to a reversionary controller. In addition to work by Barron, Lockheed, and CMU, many government agencies, industrial partners, and academia have explored technologies applicable to run time verification and assurance. However, a common, implementable framework has yet to be developed for the domain of safe and secure autonomous vehicles. The question arose, what will it take to create a run time assurance framework for the cyber physical systems in the autonomous vehicle space? To explore this question the following study investigates the key technologies available and needed to increase the reliance on run time assurance. To answer this question, four questions were provided to prominent researchers in the domains of Controls and Computer Science.

- 1) What algorithms can be used to guarantee safe bounds?

- 2) How do we create a run time version of the algorithm that enables safe switching?

- 3) How do we ensure timing constraints and worst case execution time is preserved?

4) How can model based design / simulation enable quicker realization of an end product? The first question, addressed in section 2, explores algorithms and methods suitable for creating a run time assurance argument. For an autonomous system, certain assumptions about the known environment must be made given a set of known input and output states. Utilizing these assumptions to create a boundary for non-deterministic, adaptive systems, RTA aims to achieve advanced performance with the assurance of safety constraints and failsafe operability. The bounding algorithm entails mathematical techniques within the domains of both Control Science and Computer Science to model the environment and synthesize a guaranteed boundary. The constraints can then be verified offline using known Formal Methods approaches. The scope of the bounding algorithm must be large enough to gain the added benefit of allowing the adaptive controller to safely adapt. Secondly, the bounding must incorporate all possible failure modes of what is known. A predominant focus of the bounding algorithm research is on how to synthesize a provable boundary and then how to derive a complete set of properties to ensure safety of that boundary.

The second question, addressed in section 3, investigates the ability to create a run time version of the algorithms and methods described in section 2. Creating a mathematical boundary that accounts for all possible environmental scenarios becomes a highly computationally intensive problem. Such problems are difficult to calculate offline let alone provide assurance dynamically. Once the safety properties and switching conditions are identified, one needs to develop a monitor that will calculate the switching conditions and effect the switch. It is desirable to have a general mechanism in place, which can be instantiated for many different systems that rely on the same class of properties. The mechanism can then be verified once and reused. Development of this mechanism includes the design of a runtime monitoring and switching algorithm for the chosen property language, means of initiating a switch as well as means of determining the completion of the switch. Therefore, the second domain of expertise needed to formulate the RTA framework is the ability to perform the computations at run time. As new approximation methods are being investigated to reduce the required time needed to calculate the safe boundary, methods of run time verification must be employed to ensure the right data is being monitored, at the right time, with the appropriate mechanisms to switch to a safety controller if needed. These approximation methods do not account for the overhead associated with the instrumentation of a program needed to retrieve the right set of conditions and data at the right time.

The third question, addressed in section 4, seeks to ensure timing constraints and worst case execution time is preserved. As run time methods and monitoring software is added, impacts to existing hardware and software interaction will need to be considered. For example, any run time approach for flight critical systems will need to address interactions between triplex redundant control architectures. Technologies need to be considered from a hardware timing, synchronization, and parallel monitoring approach to ensure timing is considered within and external to the system. Multiple processors, cores, or interacting systems of systems rely on consistent timing constraints being followed. In this task, specifics of the system platform are used to implement the monitoring subsystem and deploy it on the platform. For example, if a partitioned architec-

ture is used, the monitoring system may be deployed in a separate partition, which would require that inter-partition communication mechanisms have to be used for forwarding observations to the monitoring subsystem. The effect of this additional communication overhead on the system bus needs to be taken into account.

Finally, section 5 investigates how model based design / simulation enables quicker realization of RTA. Many formal verification and validation techniques emphasize correctness by construction and design for verification. These tag lines speak to the need to ensure the modeling and simulation environment is compatible with the current V&V techniques and formal methods, allowing an increase in validity in methods earlier in the design process. A modeling and simulation environment must be able to connect different abstractions of not only the run time implementation but the environment of which it is protecting. Run Time Assurance must consider such environments in order to accelerate framework production, simulation, verification, and validation.

An exploration of the currently available technology necessary to design and implement a Run Time Assurance methodology that reduces the reliance on test is, by and large, the scope of the project. The remainder of this paper documents the results of further investigation into these four questions and the challenges that arise from each.

# 2 State of the Art in Run Time Assurance Boundary Methods

Dr. George Pappas and Dr. Ratnesh Kumar

Hybrid systems combine both digital and analog components, in a way that is useful for the analysis and design of distributed, embedded control systems. Hybrid systems have been used as mathematical models for many important applications, such as automated highway systems [5, 6, 7], air traffic management systems [8, 9, 10], embedded automotive controllers [11, 12], manufacturing systems [13], chemical processes [14], robotics [15, 16], real-time communication networks, and real-time circuits [17]. Over the past fifteen years, their wide applicability has inspired a great deal of research from both control theory and theoretical computer science.

Many of the above motivating applications are *safety critical*, and require guarantees of safe operation. Consequently, much research focuses on formal *analysis* and *design* of hybrid systems. Formal analysis of hybrid systems is concerned with verifying whether a hybrid system satisfies a desired specification, like avoiding an unsafe region of the state space. The process of formal design consists of synthesizing controllers for hybrid systems in order to meet a given specification.

# 2.1 Example: Aircraft conflict resolution

As a safety critical example we consider the verification of a conflict resolution maneuver for air traffic control similar to the one described in [10]. Consider the following conflict resolution maneuver for two aircraft:

- 1. Cruise until aircraft are  $\alpha_1$  miles apart;

- 2. Change heading by  $\Delta \phi$ ; fly until lateral displacement of *d* miles achieved;

- 3. Change to original heading; fly until aircraft are  $\alpha_2$  miles apart;

- 4. Change heading by  $-\Delta\phi$ ; fly until lateral displacement of -d miles achieved;

- 5. Change to original heading.

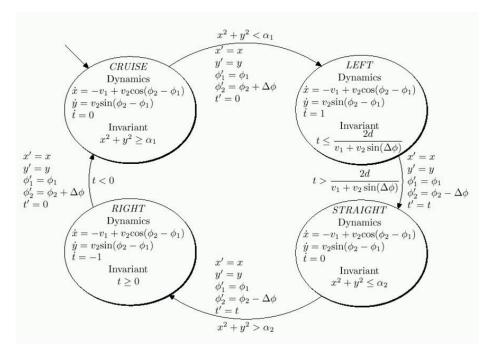

The hybrid automaton modeling this maneuver has four discrete states {*CRUISE, LEFT, STRAIGHT, RIGHT*} and is depicted in Figure 2. The continuous dynamics in each discrete state is the relative dynamics of the aircraft given a fixed velocity and heading, ( $v_i$  is the velocity and  $\phi_i$  is the heading of aircraft *i*). The aircraft are considered to be at a safe distance if they are at least 5 miles apart. In the relative coordinate frame, the *unsafe* set is given by { $(x, y) \in \mathbb{R}^2 | x^2 + y^2 \le 25$ }. Aircraft 1 is assumed to fly at a fixed velocity  $v_1$  and heading  $\phi_1$ , while aircraft 2 can switch "modes" and rotate left or right a fixed angle of  $\pm \Delta \phi$ .

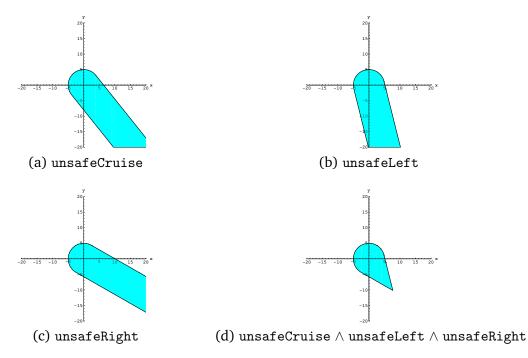

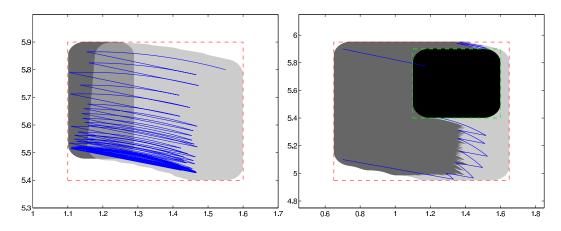

Major efforts have focused on developing algorithms that verify the safety of such hybrid system models (off-line analysis). For example, safety analysis of the hybrid system computes the region of the state space that will lead to a conflict. The result of such a computation of the minimal unsafe sets is shown in Figure 3. The set unsafeCruise \ unsafeLeft contains the set of states which are made safe by the aircraft turning left, and the set unsafeCruise \ unsafeRight contains the set of states which are made safe by the aircraft turning right. The set unsafeCruise \ (unsafeLeft  $\cup$  unsafeRight) contains the states which are made safe by turning either left or right, and the set unsafeCruise  $\cap$  unsafeLeft  $\cup$  unsafeCruise  $\cap$  unsafeLeft  $\cap$ unsafeRight shown in Figure 3(d) is the set of states which is unsafe regardless of the action the aircraft takes.

Figure 2: Hybrid system model of aircraft conflict resolution maneuver.

Figure 3: Showing minimal unsafe sets for each discrete state of maneuver automaton.

#### 2.2 Computability boundary

In developing computational approaches for hybrid system verification, the first major obstacle has to do with computability. As hybrid control systems increase to have an infinite number of states, showing that a class of verification problems is computable was challenging. A natural way to show that a class of safety verification problems is computable, is the process of *abstraction*. Given a hybrid control system and some desired property, one extracts a finite, discrete system while preserving all properties of interest. This is achieved by constructing suitable, *finite* and *computable* partitions of the state space of the hybrid control system. By obtaining discrete abstractions which are finite, and preserve properties of interest, analysis can be equivalently performed on the finite system, which requires only a finite number of steps, guaranteeing termination. Checking the desired property on the abstracted system should be *equivalent to* checking the property on the original system.

Properties about the behavior of a system over time are naturally expressible in temporal logics, such as Linear Temporal Logic (LTL) and Computation Tree Logic (CTL\*). Preserving LTL properties leads to special partitions of the state space given by *language equivalence relations*, whereas CTL\* properties are abstracted by *bisimulations*.

Unfortunately, there are severe obstacles due to undecidability. For example, in [18] it was shown that checking *reachability* (whether a certain region of the state space can be reached) is undecidable for a very simple class of hybrid systems, where the continuous dynamics involves only variables that proceed at two constant slopes. These results implied that more general classes of hybrid systems cannot have finite bisimulation or language equivalence quotients.

Therefore, exact discrete abstractions of hybrid systems is limited by this result. Given this limit, hybrid systems that can be abstracted fall into two classes. In the first class, the continuous behavior of the hybrid system must be restricted, as in the case of timed automata [19], multirate automata [20, 21], and rectangular automata [18, 22]. In the second class, the discrete behavior of the hybrid system must be restricted, as in the case of order-minimal hybrid systems [23, 24, 25].

#### 2.3 Discrete abstractions

While the decidability frontier for hybrid system verification has been well understood for some time, in most practical cases when no equivalent abstraction can be found, one may be content with a *sufficient* abstraction or an approximation, where checking the desired property on the abstracted system is sufficient for checking the property on the original system.

The basic idea is to replace the actual system by a simpler, abstract system, in which model checking is easier to perform. The verification results about the abstract system, of course, can only be related back to verification results about the original concrete system under certain conditions on how the abstract and concrete system are related and whether the particular property in question survives this abstraction process.

The options for directly constructing discrete abstractions by finite quotients and for which subclasses they work have been examined by Henzinger [26, 27]. Because of the limited scope of discrete abstractions, more general predicate abstractions [28, 29, 30, 31, 32, 33] and abstractionrefinement techniques like Counterexample-Guided Abstraction-Refinement (CEGAR) have been developed subsequently [34, 29, 35, 36]. Those directions have again worked successfully in discrete and, to some extent, real-time systems.

The use of discrete abstractions for continuous dynamics has become standard in hybrid systems verification (see e.g. [37, 38]). The main advantage of this approach is that it offers the possibility to leverage controller synthesis techniques developed in the areas of supervisory control of discrete-event systems. We briefly describe the approach presented in [39] for computing

discrete abstractions for a class of switched control systems:

$$\Sigma$$

:  $\dot{\mathbf{x}}(t) = f_{\mathbf{p}(t)}(\mathbf{x}(t)), \ \mathbf{x}(t) \in \mathbb{R}^n, \ \mathbf{p}(t) \in P$

where *P* is a finite set of modes. Given a parameter  $\tau > 0$ , we define a transition system  $T_{\tau}(\Sigma)$  that describes trajectories of duration  $\tau$  of  $\Sigma$ . This can be seen as a time sampling process. This is natural when the switching in  $\Sigma$  is determined by a time-triggered controller with period  $\tau$ .

The computation of a discrete abstraction of  $T_{\tau}(\Sigma)$  can be done by the following simple approach. We start by approximating the set of states  $X_1 = \mathbb{R}^n$  by a lattice:

$$[\mathbb{R}^n]_{\eta} = \left\{ x \in \mathbb{R}^n \ \left| \ x_i = k_i \frac{2\eta}{\sqrt{n}}, \ k_i \in \mathbb{Z}, \ i = 1, ..., n \right. \right\},\$$

where  $x_i$  is the *i*-th coordinate of x and  $\eta > 0$  is a state space discretization parameter.

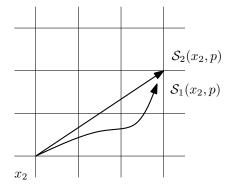

We can then define the abstraction of  $T_{\tau}(\Sigma)$  as the transition system  $T_{\tau,\eta}(\Sigma) = (X_2, U, S_2, X_2^0, Y, \mathcal{O}_2)$ , where the set of states is  $X_2 = [\mathbb{R}^n]_{\eta}$ ; the set of labels remains the same U = P; the transition relation is essentially obtained by rounding the transition relation of  $T_{\tau}(\Sigma)$  on the lattice  $[\mathbb{R}^n]_{\eta}$  (see Figure 4):

$$x'_{2} = S_{2}(x_{2}, p) \iff x'_{2} = \arg\min_{x' \in [\mathbb{R}^{n}]_{\eta}} ||x' - S_{1}(x_{2}, p)||;$$

the set of outputs remains the same  $Y = \mathbb{R}^n$ ; the observation map  $\mathcal{O}_2$  is given by  $\mathcal{O}_2(q) = q$ , the set of initial states is  $X_2^0 = [\mathbb{R}^n]_{\eta}$ . Note that the transition system  $T_{\tau,\eta}(\Sigma)$  is discrete since its sets of states and actions are respectively countable and finite.

Figure 4: Principle for the computation of a discrete abstraction of a switched system.

The approximate bisimilarity of  $T_{\tau}(\Sigma)$  and  $T_{\tau,\eta}(\Sigma)$  is related to the notion of *incremental stability* [40]. Intuitively, incremental global uniform asymptotic stability ( $\delta$ -GUAS) of a switched system means that all the trajectories associated with the same switching signal converge to the same reference trajectory independently of their initial condition. Incremental stability of a switched system can be characterized using Lyapunov functions.

**Definition 1** A smooth function  $\mathcal{V} : \mathbb{R}^n \times \mathbb{R}^n \to \mathbb{R}^+$  is a common  $\delta$ -GUAS Lyapunov function for  $\Sigma$  if there exist  $\mathcal{K}_{\infty}$  functions<sup>1</sup>  $\underline{\alpha}$ ,  $\overline{\alpha}$  and  $\kappa > 0$  such that for all  $x, y \in \mathbb{R}^n$ , for all  $p \in P$ :

$$\underline{\alpha}(\|x-y\|) \le \mathcal{V}(x,y) \le \overline{\alpha}(\|x-y\|);\\ \frac{\partial \mathcal{V}}{\partial x}(x,y) \cdot f_p(x) + \frac{\partial \mathcal{V}}{\partial y}(x,y) \cdot f_p(y) \le -\kappa \mathcal{V}(x,y).$$

<sup>&</sup>lt;sup>1</sup>A continuous function  $\gamma : \mathbb{R}^+ \to \mathbb{R}^+$  is said to belong to class  $\mathcal{K}_{\infty}$  if it is strictly increasing,  $\gamma(0) = 0$  and  $\gamma(r) \to \infty$  when  $r \to \infty$ .

Figure 5: Example of switching safety (left) and reachability (right) controllers synthesized using approximately bisimilar discrete abstractions of a model of a DC-DC converter [41, 42].

The existence of a common  $\delta$ -GUAS Lyapunov function ensures that the switched system  $\Sigma$  is incrementally stable. We need to make the supplementary assumption on the  $\delta$ -GUAS Lyapunov function that there exists a  $\mathcal{K}_{\infty}$  function  $\gamma$  such that

$$\forall x, y, z \in \mathbb{R}^n, \ |\mathcal{V}(x, y) - \mathcal{V}(x, z)| \le \gamma(\|y - z\|).$$

(1)

**Theorem 1** Consider a switched system  $\Sigma$ , time and state space sampling parameters  $\tau, \eta > 0$  and a desired precision  $\varepsilon > 0$ . If there exists a common  $\delta$ -GUAS Lyapunov function  $\mathcal{V}$  for  $\Sigma$  such that equation (1) holds and

$$\eta \le \min\left\{\gamma^{-1}\left((1 - e^{-\kappa\tau})\underline{\alpha}(\varepsilon)\right), \overline{\alpha}^{-1}\left(\underline{\alpha}(\varepsilon)\right)\right\}$$

(2)

then

$$\mathcal{R}_{\varepsilon} = \{ (x_1, x_2) \in X_1 \times X_2 | \mathcal{V}(x_1, x_2) \leq \underline{\alpha}(\varepsilon) \}$$

is an  $\varepsilon$ -approximate bisimulation relation between  $T_{\tau}(\Sigma)$  and  $T_{\tau,\eta}(\Sigma)$ . Moreover,  $T_{\tau}(\Sigma) \sim_{\varepsilon} T_{\tau,\eta}(\Sigma)$ .

Let us remark that the  $\delta$ -GUAS Lyapunov function  $\mathcal{V}$  essentially plays the role of an approximate bisimulation function here. Particularly, it should be noted that given a time sampling parameter  $\tau > 0$  and a desired precision  $\varepsilon > 0$ , it is always possible to choose  $\eta > 0$  such that equation (2) holds. This essentially means that approximately bisimilar discrete abstractions of arbitrary precision can be computed for  $T_{\tau}(\Sigma)$ .

For simplicity, we only presented results for switched systems that have a common  $\delta$ -GUAS Lyapunov function. However, let us remark that it is possible to extend these results for systems with multiple Lyapunov functions by imposing a dwell time (see [39] for more details). The approach described above has been used in [41, 42] for synthesizing safety and reachability switching controllers for a model of a DC-DC converter (see Figure 5). Similar approaches can be used to compute approximately bisimilar abstractions for incrementally stable nonlinear systems [43] and time-delay nonlinear systems [44]. An approach relaxing the incremental stability assumptions for non-linear systems can be found [45]; this approach is made currently available in the tool PES-SOA [46]. The development of discrete abstractions defined on non-uniform grids has been treated in [47, 48]. Finally, an approach for computing discrete abstractions of linear systems without griding the state-space can be found in [49].

In [30] Kumar et al. presented an approach for discretizing a hybrid system to a purely discrete transition system that preserves its behaviors at all switching instances and further preserves the structure of the underlying discrete transitions graph (transition structure of the hybrid automaton). This guarantees that the abstracted discrete transition system preserves the associated reachability/safety properties and so those can be verified using model-checking and counter-example guided abstraction refinement approaches as demonstrated in the work of Jiang [35]. This safety verification approach was applied to synchronization of distributed local clocks of the nodes on a CAN bus by Jiang et al. [36]. The class of discrete transition systems obtained by abstracting hybrid systems can themselves possess finite bisimilar abstractions, and such classes have been reported by Zhou et al. in [31, 32]. The method of abstracting hybrid systems into safety preserving discrete abstractions has further been employed by Zhou et al. [33] for abstracting Simulink/Stateflow diagrams into discrete transition systems.

#### 2.4 Reachability computations

The basic idea behind explicit-state reachability analysis is to perform a set-valued simulation of the system. Simulating the execution of a system from a single starting state up to a prespecified number of transitions is easy. It is especially efficient when the system is deterministic, because there are no choices in the simulation then.

Reachability analysis generalizes the simulation of a single initial point to simulating how a set of initial states evolves under a prespecified number of transitions of the system. Like simulations, reachability analysis directly follows the transition semantics of hybrid automata but considers appropriate sets of states instead of single states.

Reachability analysis cannot work with arbitrary sets. But suppose the initial set of states is represented by a set P of a specific family of shapes S (e.g., all polygons, or all rectangles, and so on). Suppose there is a way to compute the image of a set of states of shape S under one transition of the system and that the resulting set of states can be overapproximated again by a set of shape S. Then, for any prespecified number of transitions, say 10, the image of an initial set P of shape S under the system dynamics can be approximated by computing the one-step transition of P and then the one-step transition of the resulting set of shape S and so on until 10 transitions have been made. Since the resulting set will again have an overapproximation of shape S, the resulting procedure can be used for (approximate) bounded model checking.

The effectiveness and efficiency of this reachability analysis hinges on the computational properties of the shapes S and whether the dynamics of a particular class of systems can be approximated well by sets of shape S. The standard method to compute the reachable states is to iterate the following *one-step successor* operators for discrete and continuous transitions respectively. We now present computing such successor for two different classes of continuous dynamics.

#### 2.4.1 Zonotope methods for linear control systems

Zonotopes are a compact representation for a special form of polygons that have been used successfully for reachability analysis [51, 52, 53, 54], because their special form simplifies several aspects of reachability computation. A *zonotope*  $P \subseteq \mathbb{R}^n$  is defined by a center  $c \in \mathbb{R}^n$  and a finite number of generators  $v_1, \ldots, v_k \in \mathbb{R}^n$  that span the polytope as bounded linear combinations from the center:

$$P = \left\{ c + \sum_{i=1}^{k} \alpha_i v_i \mid \alpha_i \in [-1, 1] \right\}$$

A common denotation for this zonotope is  $(c, \langle v_1, \ldots, v_k \rangle)$ . Zonotopes are central-symmetric convex polytopes with computationally attractive features. Linear transformations, which are one of the basic operations in reachability of linear systems, can be computed efficiently for zonotopes. For a matrix  $A \in \mathbb{R}^{n \times n}$ , the image of the linear transformation  $x \mapsto Ax$  of zonotope  $P = (c, \langle v_1, \ldots, v_k \rangle)$ can simply be computed component-wise:

$$AP = (Ac, \langle Av_1, \dots, Av_k \rangle)$$

The Minkowski sum of zonotopes  $P = (c, \langle v_1, \ldots, v_k \rangle)$  and  $Q = (d, \langle w_1, \ldots, w_m \rangle)$  can also be computed efficiently by a single vector addition and a single list concatenation:

$$P \oplus Q = (c+d, \langle v_1, \dots, v_k, w_1, \dots, w_m \rangle).$$

It is also computationally efficient to find box-hull overapproximations of zonotopes.

The intersection of zonotopes with guards of hybrid automata and the regions resulting from the resets are unfortunately not generally zonotopes, which still poses challenges for using zonotope reachability for hybrid systems. The technique is extremely scalable for continuous systems with an LTI (linear time-invariant) dynamics [52, 53, 54]. Just like when working with general polytopes, direct uses of zonotope-based reachability computation suffer from the wrapping effect [53]. The wrapping effect is the effect that approximation errors accumulate during the computation, making results at higher time-steps increasingly useless. Each of these image computations may cause approximation errors. Other versions of zonotope-based reachability computation avoid wrapping effects [52], even for LTI with input, by basing all subsequent image computations on the original zonotope. This way, approximation errors may still accumulate at hybrid switching surfaces, but no longer at each intermediate time-step of a continuous transition. Extensions of zonotope-based reachability analysis to nonlinear systems and hybrid systems can be found at [55, 56]. Another pleasant property of zonotope computations is that they turn out to be numerically more stable than general polytope operations. Zonotope-based reachability computation has recently been extended to reachability computations based on support functions [57], which are essentially a generalization of zonotopes to (subclasses of) generators in infinitely many directions.

#### 2.4.2 Hamilton-Jacobi methods for nonlinear control systems

Level set methods are a class of algorithms designed for approximating the solution of the Hamilton-Jacobi partial differential equation (PDE) [58], which arises in many fields including optimal control, differential games, and dynamic implicit surfaces. In particular, dynamic implicit surfaces can be used to compute backward reachable sets and tubes for nonlinear, nondeterministic, continuous dynamic systems with control and/or disturbance inputs; in other words, inputs and parameters to the model can be treated in a worst case and/or best case fashion. The strengths and weaknesses of the Hamilton-Jacobi PDE formulation of reachability are very similar to those of viability theory: it can treat very general dynamics with adversarial inputs and can represent very general sets, but the known computational algorithms require resources that grow exponentially with the state space dimension; for example, in ToolboxLS<sup>2</sup> the level set algorithms run on a Cartesian grid of the state space. The ToolboxLS algorithms also do not guarantee the sign of computational errors, but they deliver higher accuracy for a given resolution than that available from typical sound alternatives.

Because ToolboxLS [59] is designed for dynamic implicit surfaces rather than specifically for reachability, it does not include a specialized verification interface; however, it has a 140 page user manual documenting the software and over twenty complete examples including three reachable

<sup>&</sup>lt;sup>2</sup>http://www.cs.ubc.ca/~mitchell/ToolboxLS/

set computations. It has been used primarily for reachability of systems with two to four continuous dimensions, including collision avoidance, quadrotor flips, aerial refueling, automated landing, and glidepath recapture.

The above reachability computation approach was also used by Jin et al. in [60] to demonstrate how backward reachability methods can be used to compute the stability regions and how those can then be used for switching control designs for achieving power system stability under discrete line or bus faults.

#### 2.5 Barrier certificate methods

The basic idea behind barrier certificates is to find a barrier separating reachable states and bad states that we can easily show to be impenetrable by the continuous system dynamics. Barrier certificates were proposed for safety verification in [61] and later refined in [62]. Barrier methods are different from explicit reachability computational approaches as they do not require computation of reachable sets, but instead relies on a deductive inference.

For a continuous control system, a barrier certicate is a function of state satisfying a set of inequalities on both the function itself and its Lie derivative along the flow of the system. In the state space, the zero level set of a barrier certicate separates an unsafe region from all system trajectories starting from a set of possible initial states. Therefore, the existence of such a function provides an exact certicate/proof of system safety. Similar to the Lyapunov approach for proving stability, the main idea here is to study properties of the system without the need to compute the reachable set explicitly. Although an overapproximation of the reachable set may also be used as a proof for safety, a barrier certicate can be easily used to verify safety in innite time horizon. With this methodology, it is possible to treat a large class of hybrid systems, including those with nonlinear continuous dynamics, uncertainty, and constraints. Consider a control system described by ordinary differential equations

$$\dot{x}(t) = f(x(t), d(t)), \tag{3}$$

where  $x(t) \in \mathbb{R}^n$  is the state of the system,  $d(t) \in \mathcal{D} \subseteq \mathbb{R}^m$  is a collection of uncertain disturbance inputs, and  $f \in C(\mathbb{R}^{n+m}, \mathbb{R}^n)$ . We will be mostly dealing with a bounded disturbance set  $\mathcal{D}$ . In the safety verification problem, we will be interested only in segments of system trajectories that are contained in a given set  $\mathcal{X} \subseteq \mathbb{R}^n$ . Now suppose also that a set of possible initial states  $\mathcal{X}_0 \subseteq \mathcal{X}$  and a set of unsafe states  $\mathcal{X}_u \subseteq \mathcal{X}$  are given. Our objective is to prove that the system is safe in the following sense.

**Definition 2 (Safety)** Given a system (3) and the sets  $\mathcal{X}$ ,  $\mathcal{D}$ ,  $\mathcal{X}_0$  and  $\mathcal{X}_u$ , we say that the system safety property holds if there does not exist a time instant  $T \ge 0$ , a bounded and piecewise continuous disturbance input  $d : [0,T] \to \mathcal{D}$ , and a corresponding trajectory  $x : [0,T] \to \mathbb{R}^n$  such that  $x(0) \in \mathcal{X}_0$ ,  $x(T) \in \mathcal{X}_u$ , and  $x(t) \in \mathcal{X} \ \forall t \in [0,T]$ .

The safety of the system (3) can be shown by the existence of a barrier certificate [63]. A barrier certificate is a function of state satisfying some Lyapunov-like conditions on both the function itself and its time derivative along the flow of the system, stated in Proposition 1 below. The main idea is to ask that the value of the function at the initial set  $\mathcal{X}_0$  to be non-positive, the time derivative of the function to be non-positive on  $\mathcal{X}$ , and the value of the function at the unsafe set  $\mathcal{X}_u$  to be strictly positive. If a function satisfying such a property can found, then we can conclude that no trajectory of the system starting from  $\mathcal{X}_0$  can reach  $\mathcal{X}_u$ .

**Proposition 1 ([63])** Let the system (3) and the sets  $\mathcal{X} \subseteq \mathbb{R}^n$ ,  $\mathcal{D} \subseteq \mathbb{R}^m$ ,  $\mathcal{X}_0 \subseteq \mathcal{X}$  and  $\mathcal{X}_u \subseteq \mathcal{X}$  be given, with  $f \in C(\mathbb{R}^{n+m}, \mathbb{R}^n)$ . Suppose there exists a function  $B \in C^1(\mathbb{R}^n)$  that satisfies the following conditions:

$$B(x) \le 0 \quad \forall x \in \mathcal{X}_0, \tag{4}$$

$$B(x) > 0 \quad \forall x \in \mathcal{X}_u, \tag{5}$$

$$\frac{\partial B}{\partial x}(x)f(x,d) \le 0 \quad \forall (x,d) \in \mathcal{X} \times \mathcal{D},$$

(6)

then the safety of the system (3) in the sense of Definition 2 is guaranteed.

The above method is analogous to the Lyapunov method for stability analysis. Contrary to stability analysis, however, no notion of equilibrium, stability, or convergence is required in safety verification. For example, the system does not even need to have an equilibrium.

The conditions in Proposition 1 define a convex set of barrier certificates  $\{B(x)\}$ . This is a very beneficial property, as a barrier certificate inside this set can be searched using convex optimization. For example, when the vector field f(x, d) is polynomial and the sets  $\mathcal{X}$ ,  $\mathcal{D}$ ,  $\mathcal{X}_0$ ,  $\mathcal{X}_u$  are semialgebraic, i.e., defined by polynomial inequalities and equalities, a computational framework called *sum of squares optimization* [64] that is based on semidefinite programming can be utilized to search for a polynomial barrier certificate. In particular, the software SOSTOOLS [64] is available for this computation.

The method can also be extended to handle safety verification of hybrid systems, systems with disturbances and to switching diffusion systems [62].

#### 2.6 Verification using robust simulation

Verification consists in analyzing the behavior of a control system  $\Sigma$  against some specification: given a property  $\Phi$  defined on trajectories (e.g. "a trajectory reaches the set  $Y_F$ "), we would like to be able to prove that it is satisfied by all trajectories of the control system. For discrete software/hardware systems, the problem has attracted a lot of attention in computer science, resulting in the success story of Model Checking [65] with the associated set of techniques widely used in the industry. Verification of continuous control and hybrid systems is in general much more challenging since these generally have an uncountable number of trajectories. There has also been a lot of work on the subject using set-based reachability computations, abstraction and or deductive techniques (see [66] for a recent survey).

In the following, we briefly describe an approach based on simulation of individual trajectories of a system together with the use of bisimulation function [67]. Let us consider the following dynamical system:

$$\Sigma: \begin{cases} \dot{\mathbf{x}}(t) = f(\mathbf{x}(t)), \ \mathbf{x}(t) \in \mathbb{R}^n, \ \mathbf{x}(0) \in I^0 \\ \mathbf{y}(t) = g(\mathbf{x}(t)), \ \mathbf{y}(t) \in \mathbb{R}^k. \end{cases}$$

Let  $\Phi$  be a property defined on the output trajectories y, formulated for instance in some temporal logic;  $\mathbf{y} \models \Phi$  means that trajectory y satisfies property  $\Phi$ . Let us assume that we are given a measure  $\rho(\mathbf{y}, \Phi)$  estimating how robustly property  $\Phi$  is satisfied by  $\Phi$ :

$$(\forall t \ge 0, \|\mathbf{y} - \mathbf{y}'\| \le \rho(\mathbf{y}, \Phi)) \implies \mathbf{y}' \models \Phi.$$

We refer the reader to [67] for a precise definition of such a measure and algorithms for its computation. The last ingredient of the verification approach is a bisimulation function between  $\Sigma$  and itself:

**Definition 3** Let  $\mathcal{V} : \mathbb{R}^n \times \mathbb{R}^n \to \mathbb{R}^+$  be a smooth function,  $\mathcal{V}$  is an (auto)bisimulation function of  $\Sigma$  if for all  $(x_1, x_2) \in \mathbb{R}^n \times \mathbb{R}^n$ ,

$$\mathcal{V}(x_1, x_2) \ge \|g(x_2) - g(x_1)\|$$

$$\frac{\partial \mathcal{V}(x_1, x_2)}{\partial x_1} \cdot f(x_1) + \frac{\partial \mathcal{V}(x_1, x_2)}{\partial x_2} \cdot f(x_2) \le 0$$

Using robustness measures for property satisfaction and a bisimulation function makes it possible to verify that the property holds for an infinite number of trajectories by simulating only one trajectory:

**Theorem 2** Let  $x^0 \in I^0$  be an initial condition of  $\Sigma$  and let  $\mathbf{y}$  be the associated output trajectory. Then, for all  $x'^0 \in I^0$ , with associated output trajectories  $\mathbf{y}'$

$$\left(\mathcal{V}(x^0,x'^0) \leq \rho(\mathbf{y},\Phi)\right) \implies \mathbf{y}' \models \Phi$$

The previous result allows us to verify that the property  $\Phi$  holds for all the trajectories of  $\Sigma$  by computing only a finite number of them. Let  $\{x_1^0, \ldots, x_n^0\} \subseteq I^0$  be a finite subset of initial conditions and  $\{\mathbf{y}_1, \ldots, \mathbf{y}_n\}$  the associated output trajectories of  $\Sigma$  such that for all  $x^0 \in I^0$ , there exists  $x_i^0$  such that  $\mathcal{V}(x^0, x_i^0) \leq \rho(\mathbf{y}_i, \Phi)$  then all the trajectories of  $\Sigma$  satisfy  $\Phi$ . An algorithm to construct iteratively the sample of initial states can be found in [67]. In the case we cannot cover the whole set of initial states, the algorithm identifies a subset of initial states for which the property holds.

Similar approaches have been developed for the verification of non-deterministic metric transition systems [68, 69] or hybrid systems [70, 71]. The same kind of ideas can be used for controller synthesis by defining control laws for a finite number of trajectories [72].

#### 2.7 Computational tools

Here is a current list of state of the art tools for hybrid system verification and synthesis.

• **SpaceEx** The SpaceEx tool platform (spaceex.imag.fr) developed at VERIMAG [73, 74] is a tool for computing reachability of hybrid systems with complex, high-dimensional dynamics. It can handle hybrid automata whose continuous and jump dynamics are piecewise affine with nondeterministic inputs. Nondeterministic inputs are particularly useful for modeling the approximation error when nonlinear systems are brought to piecewise affine form. SpaceEx comes with a web-based graphical user interface and a graphical model editor. Its input language facilitates the construction of complex models from automata components that can be combined to networks and parameterized to construct new components.

The analysis engine of SpaceEx combines explicit set representations (polyhedra), implicit set representations (support functions) and linear programming [75] to achieve a high scalability while maintaining high accuracy. It constructs an overapproximation of the reachable states in the form of template polyhedra. Template polyhedra are polyhedra whose faces are oriented according to a user-provided set of directions (template directions). A cover of the continuous trajectories is obtained by time-discretization with an adaptive time-step algorithm. The algorithm ensures that the approximation error in each template direction remains below a given value. Empirical measurements indicate that the complexity of the image computations is linear in the number of variables, quadratic in the number of template directions, and linear in the number of time-discretization steps.

The accuracy of the overapproximation can be increased arbitrarily by choosing smaller time steps and adding more template directions. To attain a given approximation error (in the

Hausdorff sense), the number of template directions is worst-case exponential. In case studies, the developers of SpaceEx observe that a linear number of user-specified directions, possibly augmented by a small set of 'critical' directions, often suffices. The prime goal of SpaceEx being scalability, it uses floating-point computations that do not formally guarantee soundness. SpaceEx has been used to verify continuous and hybrid systems with more than 100 continuous variables.

- **S-TALIRO** S-TaLiRo (https://sites.google.com/a/asu.edu/s-taliro/s-taliro) is a Matlab toolbox developed at Arizona State University that searches for trajectories of minimal robustness in Simulink / Stateflow. It can analyze arbitrary Simulink models or user defined functions that model the system. Among the advantages of the toolbox is the seamless integration inside the Matlab environment, which is widely used in the industry for model-based development of control software.

- **PESSOA** Pessoa (https://sites.google.com/a/cyphylab.ee.ucla.edu/pessoa/) is a software toolbox, developed at UCLA's CyPhyLab, for the synthesis of correct-by-design embedded control software. It is based on the recent notion of approximate bisimulation that allows one to replace differential equations, describing a physical system, by an equivalent finite-state machine. Controller design problems can then be solved by using efficient synthesis algorithms operating over the equivalent finite-state machine models. The resulting controllers are also finite-state, are guaranteed to enforce the control specifications on the original physical system, and can be readily transformed into bug-free code for any desired digital platform.

- **TuLiP** (http://sourceforge.net/projects/tulip-control/) developed at Cal Tech is a Pythonbased software toolbox for the synthesis of embedded control software that is provably correct with respect to an expressive subset of linear temporal logic (LTL) specifications. TuLiP combines routines for (1) finite state abstraction of control systems, (2) digital design synthesis from LTL specifications, and (3) receding horizon control. The underlying digital design synthesis routine treats the environment as adversary; hence, the resulting controller is guaranteed to be correct for any admissible environment profile. TuLiP applies the receding horizon framework, allowing the synthesis problem to be broken into a set of smaller problems, and consequently alleviating the computational complexity of the synthesis procedure, while preserving the correctness guarantee.

- LTLMOP (http://ltlmop.github.com/), developed at Cornell University, stands for Linear Temporal Logic MissiOn Planning and is a collection of Python applications for designing, testing, and implementing hybrid controllers generated automatically from task specifications written in Structured English or Temporal Logic.

- Toolbox for Level Set methods The toolbox of level set methods developed at UC Berkeley and the University of British Columbia (http://www.cs.ubc.ca/ mitchell/ToolboxLS/index.html) for solving time-dependent Hamilton-Jacobi partial differential equations (PDEs) in the Matlab programming environment. Hamilton-Jacobi and related PDEs arise in computing reachavoid operators for nonlinear control systems. The algorithms in the toolbox can be used in any number of dimensions, although computational cost makes dimensions four and higher a challenge.

- **HSolver** (http://hsolver.sourceforge.net/) [76] is an open-source software package for the formal verification of safety properties of continuous-time hybrid systems. It allows hybrid systems with non-linear ordinary differential equations and non-linear jumps assuming a

global compact domain restriction on all variables. Even though HSolver is based on fast machine-precision floating point arithmetic, it uses sound rounding, and hence the correctness of its results cannot be hampered by round-off errors. HSolver does not only verify (unbounded horizon) reachability properties of hybrid systems, but—in addition—it also computes abstractions of the input system. So, even for input systems that are unsafe, or for which exhaustive formal verification is too difficult, it will compute abstractions that can be used by other tools. For example, the abstractions could be used for guiding search for error trajectories of unsafe systems.

• **KeYmaera** (http://symbolaris.com/info/KeYmaera.html) [77, 78, 79, 80, 81] is a hybrid verification tool for hybrid systems that combines deductive, real algebraic, and computer algebraic prover technologies. It is an automated and interactive theorem prover for a natural specification and verification logic for hybrid systems. With this, the verification principle behind this tool is fundamentally different and quite complementary to existing tools. It supports differential dynamic logic [82, 77, 79, 80], which is a real-valued first-order dynamic logic for hybrid programs [82, 77, 79, 80], a program notation for hybrid systems.

### 2.8 Run-Time Assurance Framework

Run-time assurance framework provides methodologies (algorithms and tools) to ensure safe operation of a given system while maximizing the use of its certain advanced subsystem that offers complex performance capabilities but that is not fully verified. The advanced subsystem is accompanied by a substitute baseline subsystem that has lower complexity and has been verified to be fail-safe. As a result, it is possible to revert control from the advanced subsystem to the substitute baseline subsystem whenever it is deemed necessary during the run-time operation, thereby assuring safety of the overall system in a run-time fashion while maximizing the use of the advanced subsystem.

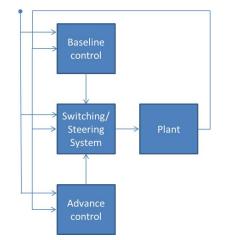

A possible architecture for run-time assurance framework is shown in Figure 6 that is inspired from the works of Barron Associates and CMU [83, 84]. Here the system under control (plant),

Figure 6: Run-time assurance architecture

a verified fail-safe baseline control and an unverified advanced control are already designed and made available. The objective is to design a switching/steering system so as to maximize the use of the advance control without sacrificing the safety of the overall system. The task of the

switching/steering system is to monitor, in an online fashion, the operation and performance of the advanced control and, if deemed necessary, switch to the fail-safe baseline control.

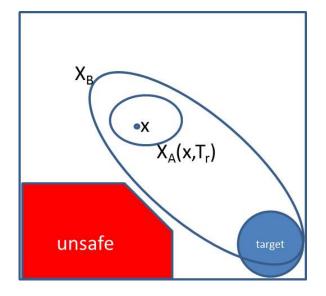

The design of a switching/steering system can be approached by modeling certain regions of the state-space as depicted in Figure 7. The figure depicts the unsafe part of the state-space, the complement of which is deemed safe. A certain subset of the safe states is depicted to be the target states; these are the states where the system is considered fail-safe (e.g., for a group of vehicles it is the set of states where the inter-vehicle distance satisfies a certain safe separation bound and also all the vehicles are stable).

Figure 7: Safety region  $X_B$  vs. active safety margin  $X_A(x,T)$

Figure 8: Enhanced safety region  $\overline{X}_B$  vs. active safety margin  $X_A(x,T)$

$X_B$  denotes the *safety region* of the baseline control, and corresponds to the set of states from where the baseline controller can steer the system to the target states while always avoiding the unsafe states, and once the target states are reached, those can be maintained forever, i.e., can be made to remain invariant. It is clear that under the operation of the advanced control, the current state x must lie within  $X_B$  (i.e.,  $x \in X_B$ ) so as to be able to avail the safety of the fail-safe baseline control by being able to safely switch to it.

Associated with any cyberphysical system, such as shown in Figure 6, is a *reaction time* T, which is the extra time needed to perform a switch in control from the instance of recognizing that such a switch is needed to the instance of actual execution of the switch. The reaction time corresponds to the computation and communication delays associated with a given cyberphysical system and needs to be computed/estimated. It then turns out that, not only the current state x must lie within  $X_B$ , but an entire "ball" of states around x that can be reached under the operation of the advanced control within the reaction time T must lie within  $X_B$ . Thus associated with the current state x and the reaction time T, exists an *active region of safety margin*, denoted  $X_A(x,T)$ , that corresponds to the set of states reachable from x within time T under the advanced control. Thus for ensuring safety, it must hold at each current state x, reached under the advanced control, that  $X_A(x,T) \subset X_B$ , and otherwise a switch to the baseline control must be made. Thus another task for the switching/steering block is to perform monitoring to the estimate the current system state and bound the set of forward reachable states  $X_A(x,T)$ .

Further, since the advanced control is unverified, it may contain faults. So further online mon-

itoring must be performed within the switching/steering block for detecting any fault in the advanced control, and a switch to the baseline control must be made once any such fault is detected. For fault-detection purposes, monitoring can be performed at multiple levels: At the advance control level to directly detect any of its faults, and also at the higher system levels to catch any advanced control faults that may manifest as failures at the higher system levels. Since not all failures at higher levels may correspond to faults in the advanced control, fault-detection must be accompanied with fault-identification. Thus a switch must be performed whenever:

$[X_A(x,T) \subsetneq X_B] \lor [$ advanced control fault detected/identified].

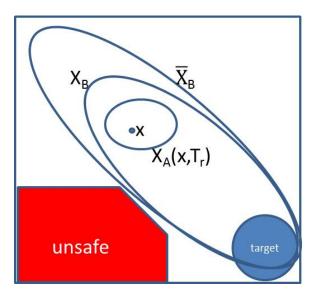

In some cases, it may be possible to enlarge the safety region  $X_B$  to a larger set  $\overline{X}_B$  by designing a steering control that can safely steer any state in  $\overline{X}_B$  to a state in  $X_B$  and retain there for at least the duration of reaction time so upon reaching  $X_B$ , the steering control may be switched to the baseline control. Thus the rule for switching from the advanced to the steering control (and next switching to the baseline control) becomes:

$[X_A(x,T) \subsetneq \overline{X}_B] \lor [$ advanced control fault detected/identified],

where the corresponding enlarged safety region  $\overline{X}_B$  is depicted in Figure 8.

In summary, the design of the switching/steering block involves the following off-line and online computations:

### Offline:

- Compute safety region  $X_B$  under baseline control

- Compute enhanced safety region  $\overline{X}_B$  under steering control

- Compute control switch reaction time  ${\cal T}$

- Verify switching/steering system

# **Runtime:**

- Estimate current state x under the operation of advanced control

- Estimate/bound active safety margin  $X_A(x,T)$  associated with advanced control at current state x within reaction time T

- Monitor input/output behaviors at various levels of hierarchy to detect any violations of the specifications for those levels

- Perform detection and identification of any advanced control fault

The following models will be needed to be able to perform the above offline/runtime computations:

- Plant model

- Baseline control model to compute/bound  $X_B$

- Real-time analysis models of cyberphysical infrastructure to estimate/bound  ${\cal T}$

- Advanced control model or its abstraction to compute/bound  $X_A(x,T)$

- Input/output correctness properties of advanced controller and its controlled plant

- Models of noise distribution

# 3 State of the Art for Runtime Monitoring and Switching

#### Dr. Insup Lee and Dr. Oleg Sokolsky

This section provides a brief overview of the current research on runtime monitoring and switching. Section 3.1 introduces runtime verification from a history perspective, and it identifies various components required for runtime monitoring and switching. Section 3.2 elaborates prior work within each component.

### 3.1 Overview of runtime monitoring and switching

Runtime verification (RV) is a relatively new area of study that is concerned with dynamic monitoring, analysis and recovery of system executions with respect to precisely specified properties. A rigorous approach to proving the correctness of programs at run time was first presented in a paradigm called program checking by Blum and Kannan [85]. The papers on program checking also demonstrated that runtime monitoring was feasible in many instances where static, designtime verification does not appear to be. This was the primary initial motivation for this field at its inception about a decade ago. That is, despite the best verification efforts, problems can occur at run time, and dynamic analysis of the running system can improve confidence in its evolving behavior.

Since then, researchers came to realize that precisely specified monitoring and checking can be used for many purposes, such as program understanding, systems usage understanding, security or safety policy monitoring, debugging, testing, verification and validation, fault protection, behavior modification (e.g., recovery), etc. At the most abstract level, a running system can be regarded as a generator of execution traces, i.e., sequences of relevant states or events. Traces can be processed in various ways, e.g., checked against formalized specifications [86], used to drive the simulation of behavioral models, analyzed with special algorithms, visualized [87], etc. Statistical analysis [88] and machine learning of system properties can be performed over the traces.

The scope of RV research covers three conceptually separate aspects. The first aspect concerns checking of traces, such as property specification, and algorithms for the checking of such property specifications over a given trace. The second aspect has to do with the generation of traces; that is, how observations are made and recorded. Most RV systems rely on some form of instrumentation to extract observations. Finally, the third aspect is about feedback and recovery; that is, actions that are carried out when a safety violation occurs, e.g., raising an alarm or switching to a safe controller.

The three aspects of RV are not independent, however. A trace generation method has to ensure that all observations necessary for checking a property are recorded. A missed observation is likely to result in an incorrect checking outcome. On the other hand, generating irrelevant observations increases checking overhead and should be avoided. Recording exactly the right set of observations for a given property is the subject of trace generation research. This dependency between the checking and trace generation aspects may also be turned around: if the trace generation method is fixed, one can pose the question, which property specification language would be the most appropriate. For example, if the trace records state changes — that is, differences between two successive states — rather than values of state variables, checking a state-based property would require an additional step of reconstructing states. Likewise, what feedback and recovery actions are required and when they must be taken depend on the checking result. A false positive checking outcome may trigger unnecessary or undesirable switching actions, whereas a false negative one prevents recovery actions from being carried out when needed, which potentially leads the system to failure.

We distinguish three broad categories of RV approaches to property specification. In the first

category, properties depend on execution history and their evaluation depends on a sequence of states in a trace. Such properties are often expressed in a variant of temporal logic; however, other specification languages are also used, such as regular expressions and state machines. The second category relies on the use of contracts or assume-guarantee interfaces between modules in the system. Properties in this category typically describe a single state or changes between two consecutive states in the trace. It may be considered a special case of the previous category. However, logics use for property specification as well as checking algorithms tend to be different here. Finally, the third category, sometimes referred to as specification-less monitoring, develops checking algorithms that detect violations of specific common properties. These properties typically relate to concurrent executions, such as freedom from race conditions [89], atomicity [90], serializability [91], etc.

An important research issue in runtime verification, which cuts across all RV aspects mentioned above, is the management of spatial and temporal overhead. An inefficient implementation of the monitoring and switching algorithm can easily be disruptive to system performance and limit the use of RV techniques. Such an implementation may also delay the system from switching to a safe state on time. A significant source of overhead is instrumentation that is necessary to extract observations from a running system. Reducing the number of instrumentation points reduces instrumentation overhead but may lead to missing observations and incorrect checking results, which may in turn result in system failure due to wrong or no recovery actions.

Last but not least, an RV framework has to provide the right feedback to the users. In many situations, it is not enough to signal that a violation has occurred. If checking is applied to a running system, as opposed to a recorded trace, feedback from the checker can help the system recover from a problem. Understanding the right feedback to produce, and reasoning about its effects on the system overall behavior is another important direction in RV research and especially critical in our RTA problem setting.

#### 3.2 Categories of runtime verification

#### 3.2.1 Monitoring and checking of temporal specifications

This category of RV tools have been developed as a direct extension of the static verification concept of model checking. Model checking algorithms [92] verify a model of the system against properties specified in a temporal logic or similar formalism. The original RV research question was whether an execution of the system can be verified at run time against the same set of properties. From the theoretical perspective, the problem is to deal with the fact that the trace is evolving as checking is being performed. Repeating the process from the beginning of the trace every time a new observation arrives is wasteful. On-line or incremental variants of the algorithms are necessary to make RV efficient. Another problem with respect to temporal properties comes from the finiteness of observed traces. Standard temporal logics, which are defined over infinite traces, and their corresponding checking algorithms need to be extended towards incomplete behaviors of finite traces.

Efficient on-line algorithms for checking a trace with respect to formulas in past- and futuretime temporal logics, as well as regular expressions, have been available for about a decade [93, 94, 95, 86, 96] and are incorporated in a variety of tools [97, 98, 99]. One of the most extensive toolsets for runtime verification of formal specifications is the MOP framework [100]. It supports a variety of specification formalisms, such as temporal logics and finite state machines, and several monitoring targets, such as Java programs and bus snooping.

Comparison of RV algorithms for different specification formalisms reveals that they have much in common. All of the algorithms maintain a checker state that is updated when new observation from a target system arrives. For example, in the case of past-time linear temporal logic (ptLTL), the checker state contains the valuations of all subformulas of a given formula in the current state of the trace, which is updated using a dynamic programming approach [95].

This similarity between algorithms for seemingly different formalisms has led to the research on special monitoring logics that can be used as the common underlying formalism for specifying monitors. Eagle [101] is a logic with explicit fixpoint operators that is capable of implementing future- and past-time temporal logics, interval logics, extended regular expressions, and other formalisms that may be useful in the monitoring context. An execution engine for Eagle specifications makes it a flexible platform for implementing checkers. RuleR [102] takes this approach one step further by replacing explicit fixed point operators with rules that activate each other in response to observations. RuleR is lower-level logic that requires more effort to encode high-level semantics of a commonly used logic. However, it allows much finer management of the checker state, leading to more efficient checkers, and yields a system that is easier to implement and maintain.

The above temporal specification languages and corresponding checking algorithms can potentially be adapted for various layers of the system, especially at the execution platform and the control layers. At the layer of execution platforms, the above temporal approaches can be applied to check for timing behaviors and other performance metrics of the tasks executing on the platform, as well as to check for correctness behavior of the scheduling and communication protocols. At the control layer, the main challenge is to derive a mapping between the specification languages specified in the control-theoretic analysis of switching (Task 1) and the logics used by the runtime monitoring algorithm. Abstractions of the state variables specified in the control-theoretic properties will be required to derive a set of observable variables (directly or indirectly) in the monitoring specification languages such that the corresponding properties can be checked efficiently. For example, if stability of the control system is expressed as an invariant of the Lyapunov functions over the control state vector; the mapping in this case provides an equivalent "invariant" in the monitoring logics on the corresponding variables observed by the monitor.

One issue in monitoring control dynamical systems is how to efficiently and accurately monitor and check their continuous state values. Along this line, temporal logics for dense-time real-values signals and corresponding automatic generation of property monitors have been explored (see e.g., [103, 104]). Temporal properties in such logics specify the required behaviors of the dynamics of purely continuous or switched control systems, such as those modeled by sets of differential equations or hybrid automata. Although the proposed monitor generation algorithm proposed in [103] works only in offline setting, extensions of such logics (e.g., to incorporate events related to signal changes) as well as adaptions of the monitor algorithm to online setting are potentially useful in the context of switching in UAVs.

From the perspective of control analysis, many properties desired for system safety such as causality and stability can be expressed in simple non-temporal invariants over frequency domain. It would be interesting to explore lightweight transformation algorithms that derive spectral values from the observed traces to leverage on the spectral properties, which will in turn enable more efficient and effective checking algorithms. This transformation approach differs from the mapping approach described above in that the checkers compute the property based on the values of the transformed control-theoretic variables instead of the directly observed values.

#### 3.2.2 Design-by-contract monitoring

Design by contract, pioneered in the Eiffel programming language [105], relies on interface specifications between components in the system. These specifications take the form of pre-conditions, post-conditions, and invariants. Contracts are typically state predicates (that is, expressions over the values of system variables in the current state). Contracts also typically allow us to relate "old" and "new" values of variables. Like any other correctness properties, contracts can be verified statically (within the inherent limitations of verification tools), but they often are also checked at run time for unexpected violations.

Unlike temporal specifications discussed earlier, contract checking is typically integrated more tightly with the system execution, and can conceptually be viewed as part of the system. Semantics of contracts determine, at which points the contracts should be checked. For example, a precondition for a method in an object-oriented program is checked when the method is called, and a post-condition is checked just before the method returns. Because of this tighter integration, instrumentation is typically not an issue.

Some languages, such as Eiffel and Spec# [106], provide special syntax for contracts. Other language frameworks support embedding of contract as code, usually providing a library of contract primitives. For example, the *Code Contracts* project [107] provides contracts for .NET languages as calls to methods of a Contract class. The TraceContract project [108] supports writing temporal specifications in Scala as calls to methods of a Monitor class. There are several comment-based contract frameworks for Java, such as JML [109] and Jass [110]. Both are based on writing specifications as special recognizable comments, which can then be extracted by tools. Some contract checking systems, Jass among them, extend standard contracts with *trace assertions* [111], which can be used to specify restrictions on sequences of invocations of methods of the class. With this extension, the distinction between contracts and temporal properties begins to disappear.

Due to the restrictive expressive power of the contract languages, design-by-contract monitoring is applicable to only simple properties. On the other hand, instrumentation and checking in this category of RV are much simpler compared to the monitoring and checking of temporal properties. Hence, this approach is potentially useful for checking component-level properties such as functional correctness, interface compliance properties (e.g., service requirements), or network communication and security protocols at the execution platform layer.

Since system-level properties are often concerned with the overall behavior of the entire system and over execution paths, they are typically not expressible by contract languages. A hybrid of the two monitoring design-by-contract and (event-triggered) temporal monitoring can help leverage the strengths of both techniques. It would be interesting to explore hierarchical monitoring, where violations at child components detected by the design-by-contract monitoring method are used as monitored events to the monitors of the parent components. An alternative hybrid technique is found in high-order temporal contracts [112]. Here, the contract systems are extended with temporal logics to express and enforce temporal properties. This integrated approach is particularly interesting as it leverages and combines techniques from both higher-order design-by-contract systems and the above first-order temporal systems within the same language.

Since contract checking is tightly integrated with the system execution, specific contract systems need to be designed for the implementation languages, which again imply language specific challanges. The tight integration of contract checking and the system execution also makes isolation of concerns between the system being monitored and the monitor itself difficult to achieve. Further, since assertions are hard to formulate for many kinds of system of interest – in particular, for adaptive systems – therefore, it may not be suitable for our setting.

#### 3.2.3 Monitoring with uncertainty and system faults

The majority of RV tools assume full observability of system states. In complex real-time embedded systems, this may not always hold true, e.g., due to the high cost in sensing all variables reliably. Uncertainty in the system behaviors also arises due to the unreliability of hardware such as due to degradation over time or possible hardware defects. It is thus useful to perform runtime verification

in presence of uncertainty in the system state information. RV techniques also need to account for the impacts of hardware and software faults on the quality of the observations.

One approach to incorporate uncertainty of the system behaviors is to use probabilistic models. In this context, the system behavior with respect to a given safety specification can be computed as the likelihood that the specification is being satisfied. A number of runtime monitoring algorithms for probabilistic properties based on statistical methods have been proposed, for instance, [113, 114, 115, 116]. Wang, *et al.* [117] extends the technique in [113] with Mont Carlo simulation for runtime verification of mixed analog and digital signal designs. Software runtime monitoring algorithms have also been extended to account for hardware behaviors [118].

To allow unobservable states in runtime monitoring, stochastic models with hidden states have been applied to the context of RV. For example, Wilcox, *et al.* [119] proposes a technique that relies on the probabilistic hierarchical constraint automata model [120] to capture probabilistic and faulty behaviors within both software and hardware. This technique integrates runtime monitoring techniques for temporal properties with HMM-based stochastic state estimation to detect safety violations during runtime. State estimation method has also been used in [121] to estimate the confidence of the verification results when sampling-based monitoring technique is used.

While existing RV tools in this category remain relatively few, uncertainty is a critical issue in complex systems such as UAVs. Integration of model-based diagnosis and other fault-tolerance techniques with runtime monitoring is a promising direction in tackling this issue. One challenge to be addressed is how to reliably derive the faulty model of the system. Since violations of the system model may violate the correctness of the monitoring algorithm itself, appropriate methods for checking at runtime the correctness of the model used are inherently necessary.

#### 3.3 Instrumentation